高效率電池的神祕面膜

作者

謝東穎簡介

謝東穎助理研究員畢業於清大材料所,目前為清大電子所博士候選人。前後任職於台積電、半導體中心及院本部國際室。2017年赴史丹福大學電機系移地研究類腦神經晶片,專長三維積體電路技術的開發,近10年有30篇的專利及論文發表。

單位

國研院台灣半導體研究中心-

標籤

-

分享文章

基於國際授權條款4.0,您可免費分享此篇文章

後摩爾定律世代(Post Moore Law Era)的來臨,使得半導體產業發展由單一微縮的方式,轉變為迎接多元創新的挑戰。半導體也從最初的實驗室規模,逐漸蓬勃發展、百家爭鳴,乃至於成為一套全球分工複雜、且極度競爭的產業。半導體中心(Taiwan Semiconductor Research Institute, TSRI)在我國的學術發展及產業創新上扮演極其重要的角色,本文將分享在後摩爾定律世代的挑戰下,三維積體電路是如何帶領產業界走向下一個高峰及其未來可能的前瞻應用。

後摩爾定律世代的挑戰

在後摩爾世代的挑戰下,人工智慧、量子電腦、下世代磁性記憶體、高速電腦、5G…等新興應用的快速崛起,臺灣面對歐美日韓等國的強勢挑戰,半導體中心(Taiwan Semiconductor Research Institute, TSRI)在我國學術發展及產業創新上的任務及角色有四大面向:「建構半導體研發平臺、支援國內學術研究、推動Å 世代科技發展、培育高階實務人才」。

電晶體的數量,決定了運算的速度。傳統上,透過從0.13微米世代、45奈米到現在的5奈米世代,都是透過微縮製程以提升電晶體數量,但在逼近物理極限時刻,這樣的方式顯得捉襟見肘,而三維積體電路則應運而生。

所謂的「三維積體電路」,製作概念上就如同在高人口密度的城市中蓋上一棟棟的摩天大樓,如圖一所示。然而,在三維積體電路中會遇到跟傳統積體電路不同的挑戰,如散熱(heat dissipation)、對準(alignment)和可靠度(reliability)的困難。此外,因不同材料間的熱膨脹係數不匹配(CTE mismatch),輕則有裂痕或脫層的現象,重則會發生基板的翹曲(warpage),這都是三維積體電路必須克服的挑戰。半導體研究中心自10年前即開始研究並著手開發相關技術,包含人工智慧晶片之關鍵技術及前瞻物聯網晶片。

圖一:三維積體電路如同在高人口密度的城市中蓋上一棟棟的摩天大樓 (Image from Pixabay)

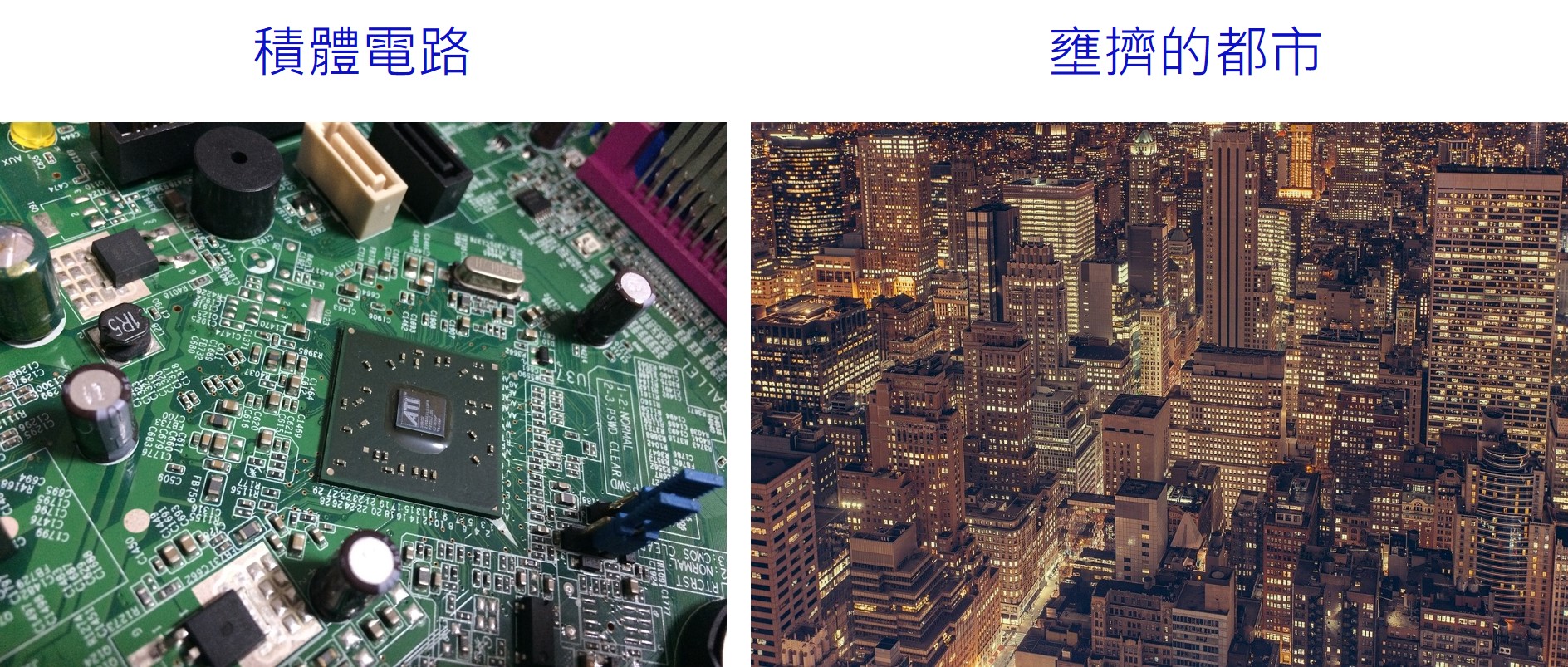

圖二:TSRI開發多年的三維積體電路技術是未來產業界突破摩爾定律的關鍵(Image from: 2016年發表於International Electron Devices Meeting)

三維積體電路之關鍵技術及亮點成果

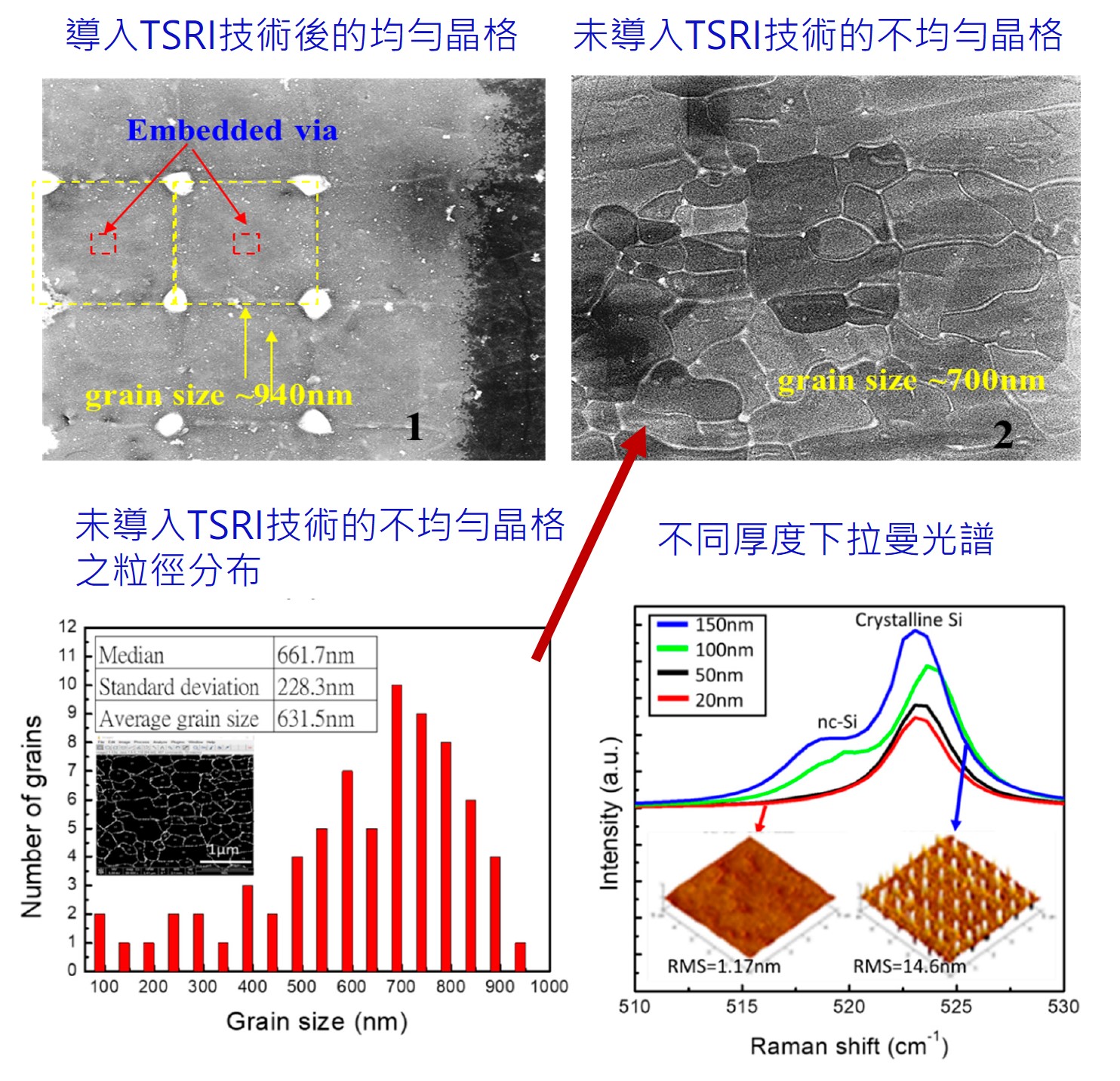

半導體中心近年重要的研究亮點包含了「奈秒綠光局部雷射」與「瞬間加熱法將非晶矽薄膜再結晶」,這些技術可用於製作三維可堆疊電晶體矽通道,完成積層型三維堆疊超薄結構電晶體(UTB transistors)、奈米線電晶體(nanowire)、奈米鰭式電晶體(FinFET)及相關積層型三維堆疊積體電路(如SRAM、 Decoder…等),相關技術將可有效緩解科學家面臨物理極限的窘迫,更是未來產業界突破摩爾定律的關鍵,如圖二所示。從科政中心2020年發表之〈我國學術能量概覽〉報告指出,透過國際合作,可使學術發表的影響力及引用量更上層樓,所以半導體中心相當重視國際合作,近年來與加州大學柏克萊分校及交大研發團隊合作,提出「前瞻晶粒邊界控制技術」,成功將雷射結晶晶粒尺寸分布從標準差228.3奈米以及平均粒徑631.5奈米,控制成均勻分布的940奈米,這個技術大大的提升元件的良率及降低元件間變異,如圖三所示。另外,半導體中心亦與清大研發團隊合作,製作記憶體內運算單元(CIM units),可用於高效能且省電之積層型三維積體電路。相關研究成果已在過去十幾年間發表於國際頂尖固態電子元件會議IEDM(International Electron Devices Meeting)及國際超大積體電路指標會議VLSI(Symposia on VLSI Technology and Circuits)。

圖三:TSRI與加州大學柏克萊分校及交大之國際合作成果-前瞻晶粒邊界控制技術發表於國際頂尖會議(IEDM)

三維積體電路的未來應用

根據2020年的〈工研院產業研討會〉趨勢分析指出,2025 年3DIC封裝占整體封裝營收將達 42.5%,國際大廠無不使出渾身解數超前佈署。從技術面來說,三維積體電路的概念可以透過不同的方式實踐,其中包含系統整合單晶片SoIC(System-on-Integrated-Chips)、整合型扇出封裝技術InFO(Integrated Fan-out)、基板上晶片封裝CoWoS(Chip On Wafer On Substrate)以及積層型(Monolithic 3DIC)等。從應用面來說,三維積體電路的應用廣且日趨重要,如平面顯示技術、自駕車、5G通訊、智慧型手機、高速運算皆是三維積體電路未來的應用舞台,而許多前瞻技術皆掌握在臺灣半導體廠商的手中,促使如Google、蘋果、超微及特斯拉等各產業龍頭,無不加碼在臺投資,可預見的是,未來臺灣在半導體的戰略地位將會更為鞏固。

延伸閱讀-科技部(科技大觀園)

訂閱電子報以獲得最新資訊

填寫連絡資訊以取得每月發行之電子報