震震有詞-離岸風能新挑戰

身處高科技發展的現代,自駕車為未來智慧終端的趨勢,等級五(不用腦)即表示自駕車輛能處理所有事情,無須人為的操作與注意。然而,等級五的自動駕駛,需要有高效能與低功率的晶片來處理即時運算以確保安全問題,為滿足此要求,晶片中的電晶體即扮演非常重要的角色,我們實驗室則致力於研究高效能且低功耗的電晶體。

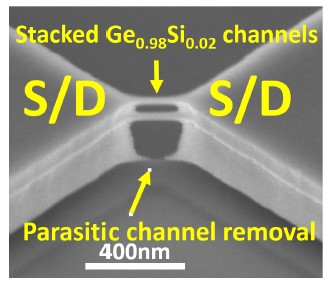

閘極環繞結構因對通道有優良的控制能力,使得元件更節能省電,具有潛力成為FinFET下一代的結構。垂直堆疊通道能提供更大的驅動電流,在未來技術節點中,具備更高效能與面積微縮的優勢。鍺(鍺矽)與矽相比,有更高的遷移率,若當作通道材料,可進一步提高元件的效能。因此,我們團隊在2019 IEDM中展示了垂直堆疊拉伸應變鍺矽(Ge0.98Si0.02)N型閘極環繞式電晶體。

在磊晶層中,鍺緩衝層在絕緣體上矽(SOI)後會經過攝氏800度的退火,限制失配差排於鍺/矽介面,增加磊晶層的品質。在攝氏350度低溫條件中成長堆疊型鍺/鍺矽磊晶結構,因為鍺與矽熱膨脹係數不同,在攝氏800度的退火時,使鍺有0.12% 拉伸應變,並使鍺矽通道磊晶層達到0.2%拉伸應變。只有2%矽在鍺矽通道,可確保電子在L valleys中且有最小的合金散射,鍺矽通道無摻雜以提升電子遷移率,鍺犧牲層有著高磷摻雜以降低源/汲極之電阻,並藉良好的光致發光以確保磊晶層有良好的品質。

在攝氏60度條件下,利用TMAH搭配超音波輔助可完整移除鍺緩衝層下的矽寄生通道。利用雙氧水搭配超音波輔助可完整移除鍺緩衝層與鍺犧牲層,最終形成兩根垂直堆疊鍺矽奈米線且無寄生通道。在通道形成後,單軸拉伸應變會增加至0.27%,因此,預估鍺矽(Ge0.98Si0.02)有較鬆弛(Relaxed)鍺高1.3倍的電子遷移率。

經過金屬後退火的元件會有閾值電壓往負偏移的現象,閾值電壓調整至零伏對低功率應用有較大的優勢。優化電子束曝光光罩,縮短通道長度至40奈米,並增加通道截面積,經過攝氏500度金屬後退火,在過驅電壓與汲極電壓等於0.5伏特時,此元件驅動電流可達48微安培(與較小通道截面積、通道長度60奈米元件相比,有3.2倍的增益),其最大電導可達136微西門子(有3.4倍的增益)。大截面積的元件相比小截面積元件需要更負的閘極電壓來完整地排空通道。在鍺N型電晶體中,此大通道截面積元件有最高的驅動電流且可與矽N型電晶體相比,並擁有(最大電導/次臨限擺幅)=8.3之最高值。

據此結果,團隊提出一種非破壞性光學方法來檢測鍺矽通道下是否有寄生通道的存在,在1310奈米紅外線照光下,沒有寄生通道的元件會有閾值電壓向負偏移的現象,然而有鍺寄生通道的元件則產生光電流。此種光學檢測方法結果與掃描電子顯微鏡之顯示結果一致。

在鍺N型電晶體中,此元件有優良的電特性(最高的驅動電流、最大電導/次臨限擺幅=8.3),高鍺含量鍺矽(Ge0.98Si0.02)通道藉由L valleys傳導與0.27%拉伸應變大幅提升驅動電流,則此元件效能可與矽通道元件相媲美。

訂閱電子報以獲得最新資訊

填寫連絡資訊以取得每月發行之電子報