衛星微型化的最後關鍵-球型馬達應用在衛星姿態控制

作者

楊智超簡介

楊智超博士任職台灣半導體研究中心(TSRI)晶片整合技術小組副研究員,研究專長包括三維積體電路開發及先進三維AI與物聯網(IoT)晶片設備。

單位

台灣半導體研究中心文章來源

Chih-Chao Yang, Tung-Ying Hsieh, Po-Tsang Huang, Kuan-Neng Chen, Wan-Chi Wu, Shih-Wei Chen, Chia-He Chang, Chang-Hong Shen, Jia-Min Shieh, Chenming Hu, Meng-Chyi Wu, and Wen-Kuan Yeh, IEEE International Electron Devices Meeting (IEDM), 2018.

Ping-Yi Hsieh, Yi-Jui Chang, Pin-Jun Chen, Chun-Liang Chen, Chih-Chao Yang, Po-Tsang Huang, Yi-Jing Chen, Chih-Ming Shen, Yu-Wei Liu, Chien-Chi Huang, Ming-Chi Tai, Wei-Chung Lo, Chang-Hong Shen, Jia-Min Shieh, Da-Chiang Chang, Kuan-Neng Chen, Wen-Kuan Yeh, and Chenming Hu, IEEE International Electron Devices Meeting (IEDM), 2019.-

標籤

-

分享文章

基於國際授權條款4.0,您可免費分享此篇文章

超越摩爾定律(More than Moore)近幾年來在世界級半導體元件會議上占有極重要的研究地位,電晶體尺寸的縮小將面臨物理極限的考驗,而積層型三維積體電路(monolithic 3DIC)即是其中解決問題最重要的工程技術之一,台灣半導體研究中心(Taiwan Semiconductor Research Institute, TSRI)自2010年開始研究此相關技術,係開發前瞻物聯網晶片與人工智慧晶片之關鍵技術。

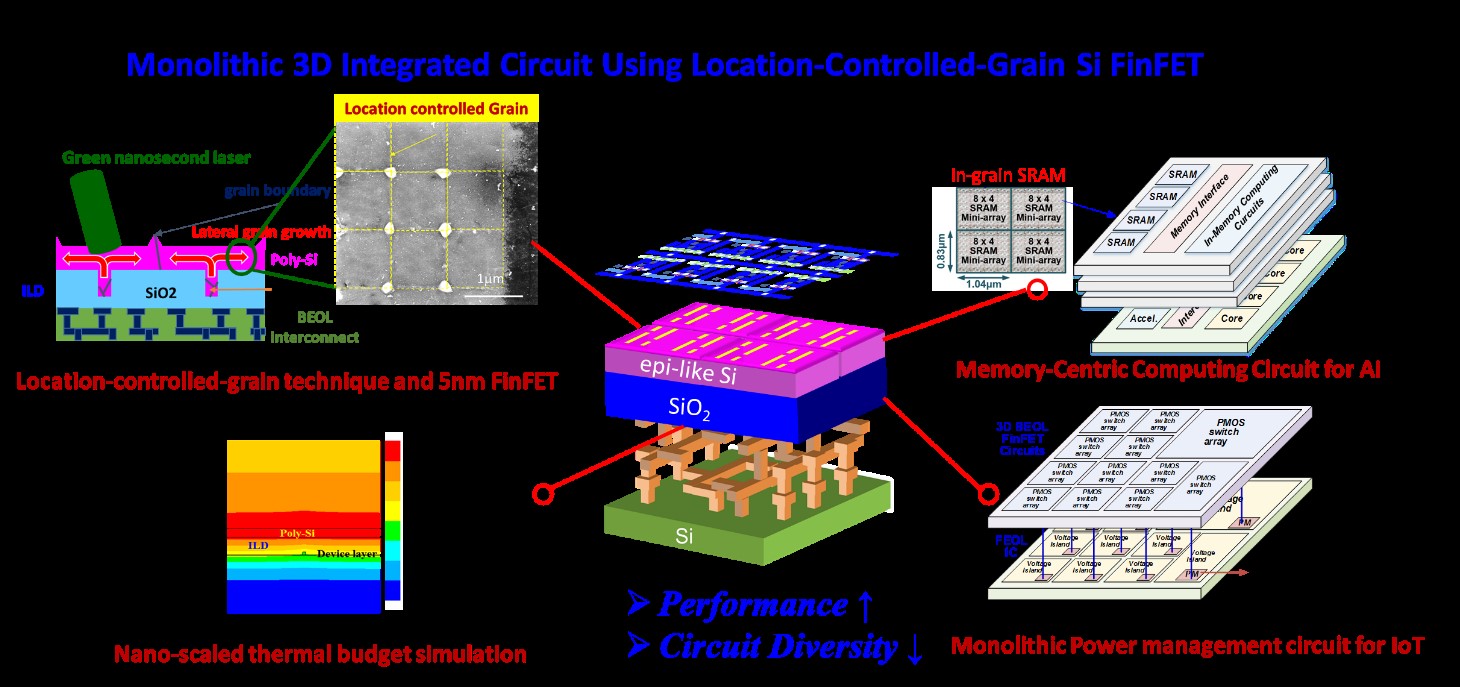

利用奈秒綠光雷射局部與瞬間加熱法將非晶矽薄膜再結晶,可用於製作三維可堆疊電晶體矽通道,完成積層型三維堆疊超薄結構電晶體(UTB transistors)、奈米線電晶體(Nanowire)、奈米鰭式電晶體(FinFET)及相關積層型三維堆疊積體電路(如SRAM、 Decoder…等),近年來TSRI團隊更和交通大學胡正明院士及陳冠能教授研發團隊合作提出前瞻晶粒邊界控制技術,以及與清華大學張孟凡教授研發團隊合作製作記憶體內運算單元(CIM units),可用於高效能且省電之積層型三維積體電路。相關研究成果已在2012至2019年間發表二十餘篇論文於國際頂尖固態電子元件會議IEDM(International Electron Devices Meeting)及國際超大積體電路指標會議VLSI(Very large-scale integration),並與世界頂尖半導體研發團隊及半導體晶片製造公司同場發表研究成果,TSRI研發團隊持續與國內學術單位及台灣的半導體產業界合作,創新研發技術及提供服務平台,將為台灣積體電路學研的發展,扮演重要協助腳色。

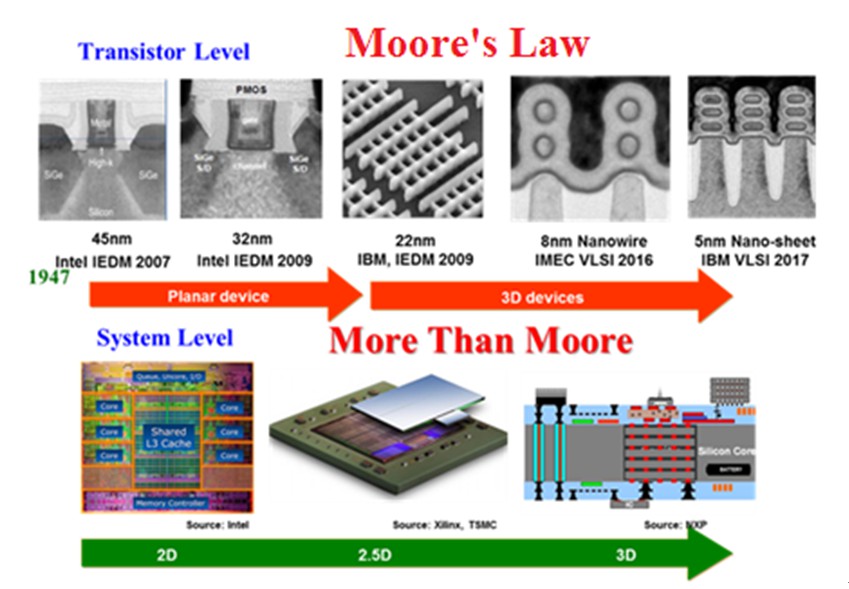

圖一:摩爾定律(Moore’s Law)與超越摩爾定律(More than Moore)

超越摩爾定律(More than Moore)近幾年來在世界級半導體元件會議上占有極重要的研究地位。摩爾定律下,電晶體尺寸的縮小將面臨物理極限的考驗,而製程中三維(3D)堆疊電晶體即是其中解決問題最重要的方法之一,藉由垂直疊加各晶片層,進而提高單位面積的元件數量及整合不同功能元件,使得製作成本下降,而金屬導線連線距離也可因此而縮短,減少電子訊號的延遲,滿足物聯網晶片與人工智慧晶片高速且省電的需求。然而,半導體晶片製造過程中,垂直疊加電晶體元件的過程有其限制,一般的半導體高溫製程將破壞電晶體及金屬連導線,大幅降低半導體晶片成品的良率。

為克服此問題,由於雷射熱擴散深度僅有數百奈米,以雷射表面加熱技術製作之低溫多晶矽(poly-Si)材料,相當適合作為三維堆疊電晶體的開發,更重要的是其製程簡單且便宜。然而多數以多晶矽做為電子元件的物理及電特性並不如結晶矽來得好,主要原因在於晶粒內與晶粒邊界(Grain boundary)的缺陷對半導體元件電性來說是一個很嚴重的問題,因此如何將多晶矽材料品質提升至與結晶矽接近或形成可控制之單晶顆粒,對於製作積層型三維堆疊電晶體是一項非常重要的課題。

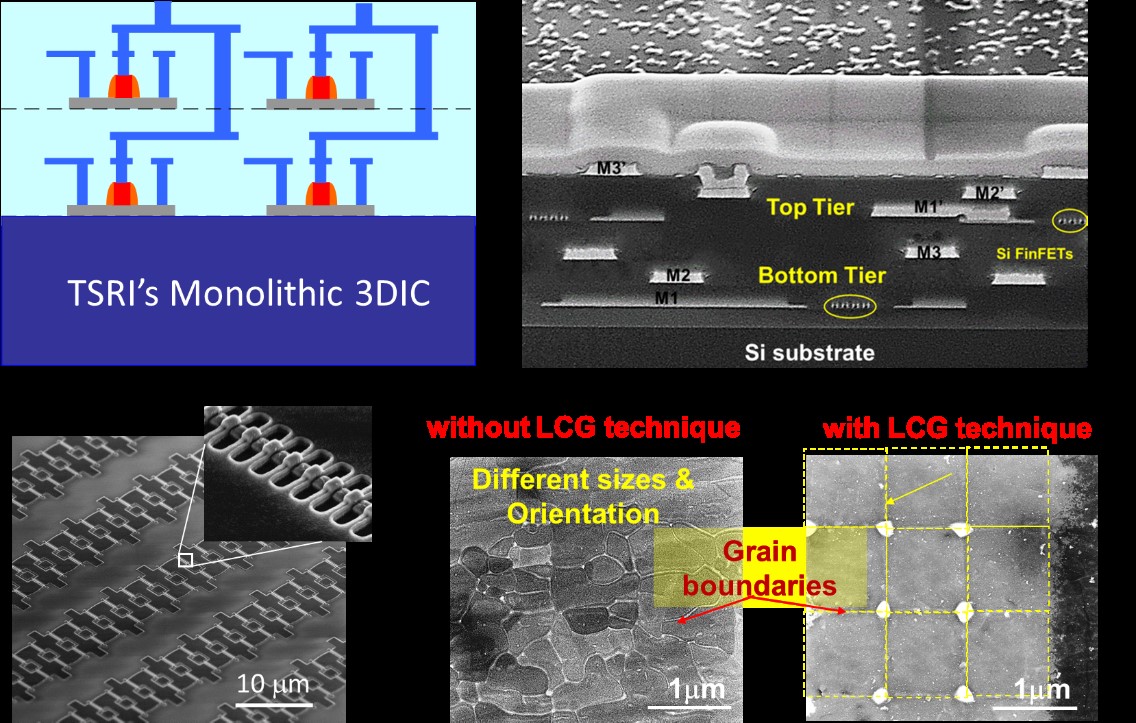

圖二:積層型三維堆疊晶片技術與奈米鰭式電晶體應用晶粒邊界控制技術之比較

台灣半導體研究中心(TSRI)研究團隊利用奈秒綠光雷射局部與瞬間加熱法將非晶矽薄膜再結晶,用於製作可三維堆疊矽通道,完成積層型三維堆疊超薄結構電晶體(UTB transistors)、奈米線電晶體(Nanowire)、奈米鰭式電晶體(FinFET)及相關積層型三維堆疊積體電路(如SRAM、Decoder…等)研發,近年來和交通大學胡正明院士及陳冠能教授共同合作,提出一種晶粒邊界控制技術(Location-controlled-grain Technique),可用於製造三維可堆疊單晶粒矽通道,其係先在絕緣層上蝕刻出可控制規則之孔洞(via hole),並利用奈秒綠光雷射局部與瞬間加熱將非晶矽薄膜再結晶,以孔洞結構為中心向外側延伸成長為單晶粒矽(single grain Si),如此製作之積層型奈米鰭式電晶體(FinFETs),可大幅提高晶片效能與良率。團隊也與清華大學張孟凡教授研發團隊合作開發記憶體內運算單元(Computing in memory),研發製作人工智慧晶片雛型單元,相關研究成果已在2012至2019年間發表二十餘篇論文於國際頂尖固態電子元件會議(IEDM)及國際超大積體電路指標會議(VLSI),與世界頂尖半導體研發團隊及半導體晶片製造公司同場發表研究最新成果。

TSRI研究團隊長期支援國家大型研發計畫(包括各大型人工智慧晶片與物聯網晶片計畫、教育部高教深耕計畫、科技部半導體射月計畫及奈米科技創新應用主軸計畫等),協助開發具量產價值之雛型產品,提供學界客製化積體電路製造技術,持續與國內學術單位及台灣的半導體產業界合作,創新研發技術及服務平台,為台灣積體電路學研的發展,扮演重要協助腳色。

訂閱電子報以獲得最新資訊

填寫連絡資訊以取得每月發行之電子報