新冠肺炎(COVID-19)防疫急迫需求—超靈敏雙抗體快篩試劑

作者

張廖貴術簡介

張廖貴術教授任職於國立清華大學工程與系統科學系,研究專長為超大型積體電路與快閃記憶體元件與製程。張廖教授為IEEE特聘獎者,並曾於2012-2015年擔任期刊IEEE Electron Device Letters之編輯。

單位

國立清華大學文章來源

IEEE Electron Device Letters, vol. 40(2), pp. 181-184, 2019.https://ieeexplore.ieee.org/document/8981803-

標籤

-

分享文章

基於國際授權條款4.0,您可免費分享此篇文章

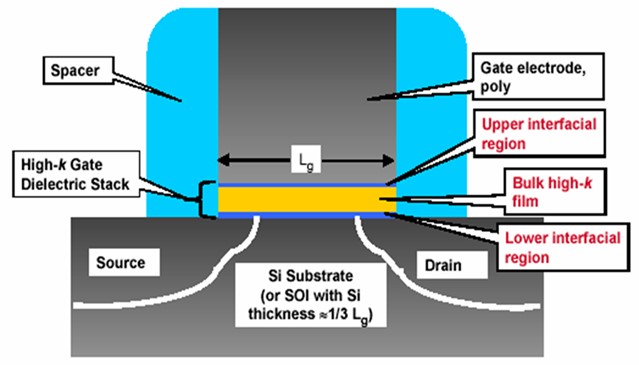

金氧半場效電晶體(MOSFET)是積體電路(IC)中最常見的半導體元件。MOSFET的通道和閘極堆疊之研究開發是實現高性能IC的關鍵技術。據文獻報導,SiGe超晶格(SL)通道可以增強MOSFET中的載子遷移率,因此本研究探討具有SiGe和類似SiGe SL通道的鰭式場效電晶體(FinFET)電特性,研究結果顯示,SL結構增強了具有SiGe通道的n型FinFET之電子遷移率,還實現了更高的導通電流和導通/關閉電流比。此外,通過在GeO2界面層(IL)上進行氫電漿(H*)處理,可以在p基底Ge (pGe)金氧半(MOS)元件中同時實現低等效氧化層厚度和低閘極漏電流密度。研究發現GeO2 IL中低氧化態的GeOx去除對pGe MOS元件的電特性有非常重要的影響。通過H*處理,具有高氧化態的GeO2 IL改善了電特性和可靠性,因此,SiGe SL通道和經過H*處理的GeO2 IL很有機會應用於實現高性能Ge MOS元件。

金屬氧化物半導體場效電晶體(MOSFET)是數位和類比電路中最常見的半導體元件,也是最常見的功率元件。它是第一個真正的小型電晶體,經由小型化和批量生產可以實現廣泛的應用,其縮小和微小化也一直在促進積體電路(IC)技術指數增長。MOSFET中需要具有高載子遷移率的通道和具有低等效氧化層厚度(EOT)的閘極介電層,以實現高性能IC。因此,通道和閘極堆疊工程的研究與開發是實現高性能IC元件最關鍵的製程技術。

鰭式場效電晶體(FinFET)已超越一般平面MOSFET元件而被廣泛應用,以遵循摩爾定律。然而,對於Si基材的FinFET技術,載子遷移率仍然是最重要的問題。由於Ge可以提供較Si高的載子遷移率,因此使用Si / Ge異質結構通道可以實現高性能MOSFET。但是由於Si / Ge異質結構通道很難在鰭型通道表面上磊晶成長,因此很少在FinFET上使用。磊晶矽鍺(Epi-SiGe)通道厚度如果大於其臨界厚度,則可能會在SiGe通道中產生缺陷。文獻指出,以SiGe超晶格(SL)結構用作MOSFET的元件通道,將獲得具有更少缺陷和更好界面品質的通道,因為SL結構中每個Epi-Si / Ge都非常薄,且低於Epi-Si / Ge臨界厚度,因此,SiGe SL通道可以提高MOSFET的載子遷移率;然而卻很少文獻報導SiGe在n型通道FinFET的應用。

除此之外,通過O2後電漿氧化處理Ge金氧半(MOS)元件實現了低EOT,但是GeO2界面層(IL)也可能限制了EOT的縮減。隨著EOT值縮小到0.6 nm,閘極漏電流密度(JG)將十分高。與GeO2相比,低氧化態的GeOx具有較小的能隙且可能使JG增加。另外,當在Ge基底表面上沒有保留GeO2 IL時,界面品質可能顯著降低或表面粗糙度增加,因此,GeO2 IL工程是實現低EOT和JG並提高Ge MOS元件界面品質的最關鍵製程。由於GeO2是一種熱不穩定材料,很容易分解為GeOx(1

總而言之,具有SiGe SL通道的FinFET元件顯示出更高的電子遷移率,以及導通電流和導通/關閉電流比。此外,在熱生長的GeO2 IL上進行H*處理,可以同時實現低EOT,低JG,低頻率分散,低邊界陷阱密度和更好的元件可靠性,也不影響磁滯和界面陷阱特性。因此,SiGe SL通道和GeOx IL上的H *處理將很有希望應用於高性能Ge MOS元件製程。

延伸閱讀-科技部(科技大觀園)

訂閱電子報以獲得最新資訊

填寫連絡資訊以取得每月發行之電子報